中國粉體網訊 近年來,隨著5G、可穿戴設備、智能手機、汽車電子、人工智能等新興領域蓬勃興起,集成電路應用正向著多元化應用方向發展,先進三維封裝技術也逐漸成為實現電子產品小型化、輕質化、多功能化的重要手段。玻璃通孔(TGV)互連技術具有高頻電學特性優異、成本低、工藝流程簡單、機械穩定性強等應用優勢,在射頻器件、微機電系統(MEMS)封裝、光電系統集成等領域具有廣泛的應用前景。

玻璃通孔(TGV)互連技術主要包括成孔技術、填孔技術和高密度布線,高密度布線可以實現最終的電氣連接。電子設備的小型化和便攜化是重要的發展趨勢。玻璃基板高密度布線技術可以將更多的電路功能集成在更小的玻璃基板上,減少電子設備的體積和重量,滿足不同應用場景對設備小型化的要求,提高設備的便攜性和適用性。但由于半加成工藝法在線寬小于5μm的時候會面臨許多挑戰,例如在窄間距內刻蝕種子層容易對銅走線造成損傷且窄間距里的種子層殘留易造成漏電,因此針對玻璃基板的表面高密度布線,學界也有不同工藝路線的探索。

線路轉移(CTT)和光敏介質嵌入(PTE)

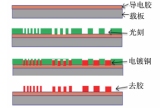

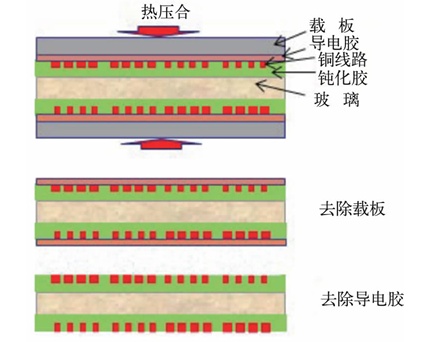

劉富漢等開發了CTT和PTE技術。CTT主要包括精細重布線層(RDL)線預制和將RDL集成到基板上兩個過程。每一RDL可以在可移動載體上單獨制造一層薄導電層,并在轉移到基板上之前測試或檢查細線成品率,精細線路的形成采用細線光刻和電解鍍銅的方法,并且以薄銅箔作為鍍層的種子層。

線路轉移過程 來源:Liu.Advances in embedded traces for 1.5 μm RDL on 2.5D glass interposers.

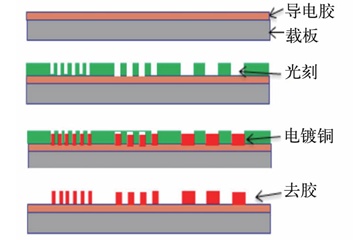

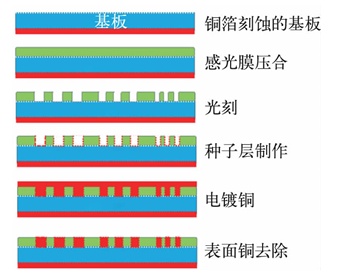

PTE工藝首先刻蝕基板下側銅箔,并使用真空壓膜機在基板上側壓合感光膜,采用物理氣相沉積(PVD)分別沉積Ti和Cu作為阻擋層和種子層,接著采用電鍍工藝填充溝槽,溝槽填充完后,使用化學腐蝕劑刻蝕掉上表面的銅從而露出線路。

PTE工藝流程 來源:Liu.Advances in embedded traces for 1.5 μm RDL on 2.5D glass interposers.

多層RDL的2.5D玻璃轉接板技術

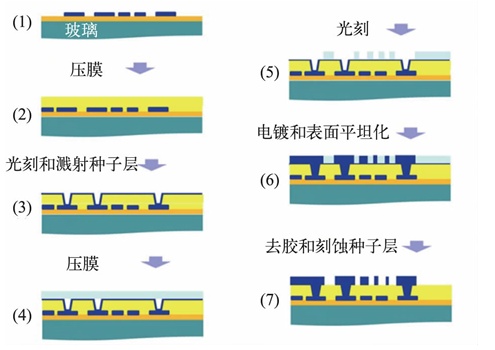

喬治亞理工學院的Lu等研究了多層RDL的2.5D玻璃轉接板技術,實現了面板級光刻后1.5~5μm的線條溝槽制備,并提出改進式半加成工藝法(SAP),達到了5μm以下低成本的線寬制作工藝。工藝流程為在第一層RDL的基礎上進行壓膜,然后通過顯影制作通孔并暴露出第一層RDL的銅焊盤,接著進行種子層濺射。濺射完成后,將高分辨率的光刻薄膜層壓在基板上側并進行高精度的曝光、顯影。完成上述步驟后,采用電鍍工藝填充通孔并用旋轉金剛刀進行表面平坦化,最后去除光刻薄膜并完成種子層刻蝕。

多層RDL的工藝流程 來源:Lu.Advances in panel scalable planarization and high throughput differential seed layer etching processes for multilayer RDL at 20 micron I/O pitch for 2.5D glass interposers.

參考來源:

Lu.Advances in panel scalable planarization and high throughput differential seed layer etching processes for multilayer RDL at 20 micron I/O pitch for 2.5D glass interposers.

Liu.Advances in embedded traces for 1.5 μm RDL on 2.5D glass interposers.

陳力.玻璃通孔技術研究進展

(中國粉體網編輯整理/月明)

注:圖片非商業用途,存在侵權告知刪除!